自動運転向けアクセラレータのアーキテクチャ

5.8K Views

April 28, 22

スライド概要

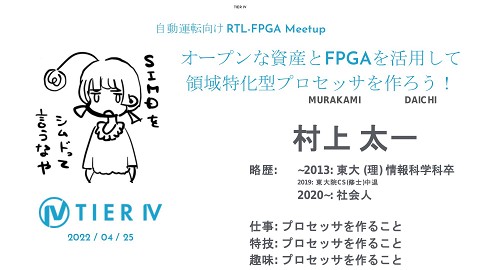

2022/4/25に開催した「TIER IV 自動運転向け RTL-FPGA 開発 テックミートアップ」の資料です。

関連スライド

各ページのテキスト

自動運転向けアクセラレータのアーキテクチャ 塩谷 亮太

塩谷 亮太(しおや りょうた) ◼ 所属: ◇ 東京大学 情報理工学系研究科 創造情報学専攻 (准教授) ◇ ティアフォーには技術アドバイザーとして参加 ◼ 専門:コンピュータ・アーキテクチャや基盤ソフトウェア ◇ 特に CPU のマイクロアーキテクチャ ◇ 最近は言語処理系やセキュリティ関係の研究も多いです 2

背景:自動運転アルゴリズムと消費電力 ◼ 背景:アルゴリズムの発展と,消費電力の肥大化 ◇ 現状でも高性能な CPU や GPU を使って処理する必要がある ◇ 「スーパーコンピュータを背負って走っている」とも ◇ 今後もさらに処理量が肥大化し続ける見込み ◼ 課題 1. 実際に売る車に搭載しようと思うと,相当に消費電力を削減してい く必要がある 2. アルゴリズムの発展へ柔軟に対応する必要がある ◼ そのためのハードウェアを研究・開発中 ◇ 方針:処理ごとに特化したアクセラレータで消費電力を減らす 3

アクセラレータをどう作る? ◼ ASIC/FPGA 上で専用回路を作る? ◇ 開発が大変で時間もかかるし柔軟性もない ◼ 方針:専用回路ではなくプロセッサにする 1. 共通のプロセッサのフレームワークを作る 2. 処理対象ごとにプロセッサ構成をカスタマイズする 4

Application Specific SIMT (AS-SIMT) 1. Single-Instruction Multiple-Thread (SIMT) アーキテクチャをベースに ◇ NVIDIA の GPU 等で採用されている ◇ 基本的な構造は 1980 年代の Pixar Image Computer にも 2. 処理の部分ごとにカスタマイズ ◇ カスタマイズにより自動運転に出てくる処理を効率良く広くカバー ◇ 3~4パターンのプロセッサがあれば大体カバーできる 3. RISC-V ベース ◇ SIMT は,プログラムからはただのマルチプロセッサに見える ◇ 既存の RISC-V ツールチェインをほぼそのまま流用できる 5

自動運転のプログラム(の重たい部分)に 期待できる性質 ◼ 大量のデータに(ほぼ)同じ処理を施す ◇ 個々の処理自体は比較的簡単 ◇ 単純な行列演算や画像処理ほどには簡単ではない ☐ 適応的な処理やツリーのトラバーサルなどがよくある センサー処理/自己(位置)認識 推定/計画/制御 // 200,000 parallel for each data in sensor frame { data_out[i] = A*data[i] + B; if (DownSample(data[i])) { remove(data_out[i]); } } // 90,000 parallel for (i = 1 to 300) { for (j = 1 to 300) { Q[i][j] = A[i] * B[j]; } } while (matching score < target score){ // 2,000 parallel for each point in Processed Data { voxels = find_near_voxels_in_map(map, point); scores = A*point + B; [update hessian matrix] } Matching score = gather (scores); pose = update_by_newton method; } // Quadratic Programming (Newton-Method + LP) while (not optimized) { A = LU; // LU Decomposition (SIMD) [linear programming] (SIMD) [Update Hessian] (SIMD) } 6

SIMD(Single Instruction Multiple Data) ◼ 単一の命令で複数のデータを演算(複数の演算器を駆動) ◇ 命令メモリやデコードなどの制御ハードが省ける ◇ 多数のデータに似たような処理をする場合によく採用される ◼ ループの並列実行 ◇ イタレーションをスレッドとしてマルチスレッド実行 ◇ 全スレッドが同じプログラムを実行 = PC や命令メモリ部分は共通化できる スカラ CPU(のマルチコア) SIMD アーキテクチャ PC PC PC PC 命令メモリ 命令メモリ 命令メモリ 命令メモリ レジスタ レジスタ レジスタ 演算器 演算器 演算器 レジスタ レジスタ レジスタ 演算器 演算器 演算器 7

SIMT(Single Instruction Multiple Thread) ◼ SIMD だと,全ての演算器は全く同じ動きしかできない ◇ スレッドごとに個別に分岐ができない ◼ SIMT アーキテクチャ:各スレッドごとに違う PC を用意 ◇ 全員が同じパスにいる限りは SIMD と同じように動作 ◇ 分岐して違うパスにいった場合は,それぞれ時分割して処理 ◇ 各スレッドで動作するのは普通のシングルスレッド・プログラム SIMD アーキテクチャ SIMT アーキテクチャ PC PC PC PC 命令メモリ 命令メモリ レジスタ レジスタ レジスタ レジスタ レジスタ レジスタ 演算器 演算器 演算器 演算器 演算器 演算器 8

ハードウェアの効率 ◼ 実際に演算を行っている部分(図の赤い部分)の比率を上げることが重要 ◇ 速度:同じチップ面積により多くの演算器を積めると性能が向上 ◇ 電力:演算以外のことをする回路が減ると電力効率が上がる ☐ 消費電力は回路面積におおむね比例 ◼ 一方で,演算以外の回路は柔軟性に直結する ◇ 命令がばらばらに動けるとか,レジスタが多いとか マルチコア SIMD/SIMT 行列演算器を持つ SIMD/SIMT 命令 レジスタ 演算器 9

カスタマイズと電力効率 ◼ 相反する要求 ◇ 実際に演算を行っている部分の比率を上げることが重要 ◇ 一方で,演算以外の回路は柔軟性(対応できるアプリの多さ)に 直結する ◼ アプリごとに SIMT アーキテクチャのパラメータを変える事で対応 ◇ 同時に動くスレッドの幅(空間方向と時間方向のそれぞれ) ◇ 搭載する演算器の選択(FP あり/なし,専用演算器の追加) ◇ パイプライン段数 10

RISC-V ベース ◼ SIMT は,プログラムからはただのマルチプロセッサに見える ◇ 既存の RISC-V ツールチェインをほぼそのまま流用できる ◼ RISC-V はカスタマイズも容易 ◇ FP 命令の有無,専用命令の追加など 11

AS-SIMT の狙い ◼ 狙い ◇ 電力効率の向上 ☐ アプリごとにカスタマイズ ◇ 高い柔軟性 ☐ SIMT によるプロセッサ構造 ◇ 開発コストの削減 ☐ フレームワークからの派生によるハードウェア設計の簡素化 ☐ ソフトウェアスタックの流用 ◼ 作り込んだ専用回路には,当然電力効率は及ばない ◇ CPU や GPU より十分に効率が良く,かつ柔軟性と低コストを兼 ね備えた部分を狙う ◼ 実装などは,次の発表に続きます 12